Automatic routing of PCBs is an interesting topological problem and various approaches exist for doing it.

Both mainline gEDA PCB and pcb-rnd support simple autorouting of selected rats with the "Connects->Auto-route selected rats" menu option.

The "rats" are simply the flying wires indicating connectivity in the absence of copper trackwork, polygons or pours to complete the connection.

We begin with an example of automatic tracks laid down by the default autorouter in gEDA PCB and pcb-rnd.

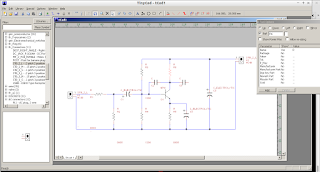

We start with a layout showing the components and rats

After running the built in autorouter, we get the following

As can be seen, the autorouting gives a functional result, although arcs and forty-five degree corners are not supported.

The code for gEDA PCB has included Specctra .DSN and .SES file export and import for some time.

The Specctra import and export code was reviewed and tested in the pcb-rnd fork to allow pcb-rnd to work with the Java application "Freerouting", written by Alfons Wirtz. "Freerouting" has been used for some time by KiCad's pcbnew application for its autorouting.

Further details about the history of the Freerouting software can be found at

http://www.freerouting.net/

"Specctra" is simply a proprietary name for a set of file formats that allow interchange of electronic designs between applications, and is not uncommon as an interchange format for autorouters. Specctra files are essentially an s-expression format description of a PCB layout.

A Specctra .DSN file describes an entire layout, whereas the .SES (session) file describes the incremental change over and above a reference or initial .DSN described design.

Freerouting was obtained from the following github repository, which includes a precompiled .jar file which can be run easily from the command line if a Java virtual machine is installed.

https://github.com/freerouting/freerouting

Quirks in the Freerouting code include an improperly escaped " character, i.e.

(pcb notnamed

(parser

(string_quote ")

(space_in_quoted_tokens on)

(host_cad "gEDA pcb-rnd")

(host_version "1.2.0")

)

and also exporting in mm rather than microns in the .DSN export; although it exports in microns in the .SES export. After these issues were addressed, loading worked without issue.

DSN export from pcb-rnd was tested, and exported files were found to load without difficulty in the Freerouting utility.

Autorouting was initiated in Freerouting, and it proceeded to autoroute the layout without fuss.

The modified .DSN file was then exported from Freerouting and with some additional code (see

pcb-rnd svn) addressing the aforementioned quirks, the .DSN file was able to be loaded into pcb-rnd for comparison with the original layout

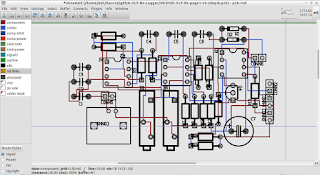

Having confirmed the ability to export, process and reload the .DSN file, further testing was undertaken with an existing design to allow a quick comparison with the inbuilt autorouting.

Again, starting with the same simple layout as before, which was used to demonstrate the built-in autorouting...

...a .DSN file was exported with the "File->Export Layout..." menu item

This was then loaded into the java Freerouter and quickly autorouted

A .SES session file was then exported with the "File->Export Specctra Session File" menu item in Freerouter, which was then loaded in pcb-rnd using the ":LoadDsnFrom(filename)" command

...at which point the newly created routes appeared on the existing layout, along with the rats

After hitting "o" to sort out the remaining rats, the layout looked like this:

As can be seen, the Freerouting software generates 45 degree angles by default, unlike the built in autorouter. Freerouting can also work with free angles and other options selectable in its menu system.

Further testing is encouraged, and time spent with Freerouting will likely allow more if its features to be utilised.

The new code in

pcb-rnd can currently be obtained via svn, at

although the next major release of pcb-rnd as a debian/ubuntu package will include these enhancements.

Coding is now underway to allow importing of

MUCS autorouter designs, which will allow an additional router to be used with pcb-rnd in the near future. Here is a screenshot of some vias being imported from a MUCS test layout:

A bit more code, and tracks are importing too...

Testing of the standalone C++ autorouter

https://github.com/vygr/C-PCB is also planned... once my C++14 toolchain starts to behave.... since it also imports and exports .DSN format layouts, adding yet another autorouting option to pcb-rnd.

The small autorouted example board was actually made with the gEDA toolchain prior to the new autorouter support. Being a fairly simple design, the layout was hand-routed, and the resulting layout can be seen in gerbv, the gEDA project gerber viewer:

And here's the board, as delivered

KiCad users may recognise some of the footprint silkscreen elements, which were ported from KiCad modules with the

translate2geda and

kicadModuleToGEDA utilities. Of course, pcb-rnd can load and save KiCad Layouts with embedded modules too, which can then be saved in gEDA PCB/pcb-rnd format if desired.

Oh, I nearly forgot to mention it....